Olá,

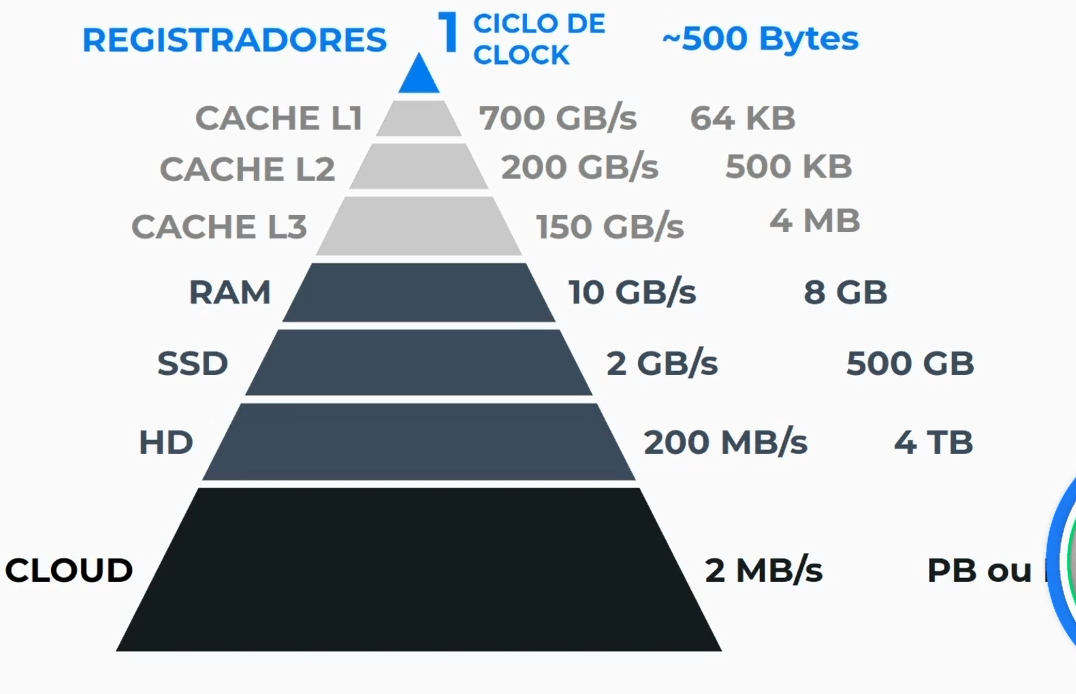

O instrutor explicou que acessamos o registrador a 1 ciclo de clock (~500 Bytes) e a L1 a 700 GB/s (64KB) porém não entendi de onde vem essa velocidade de acesso que pode variar dependendo da memória que está sendo acessada.

Olá,

O instrutor explicou que acessamos o registrador a 1 ciclo de clock (~500 Bytes) e a L1 a 700 GB/s (64KB) porém não entendi de onde vem essa velocidade de acesso que pode variar dependendo da memória que está sendo acessada.

Oii, Gabriel! Como vai?

Agradeço por aguardar o nosso retorno.

Obrigada por compartilhar sua dúvida aqui no fórum, ela poderá ajudar outros alunos e alunas que estejam com a mesma dúvida e vem explorar o fórum em busca de uma explicação.

Pois bem, a localização da velocidade de memória vai depender de alguns fatores, temos que levar em consideração o tipo de tecnologia utilizada, a largura de barramento de dados, a frequência do clock do processador e a organização da hierarquia de cache.

Podemos usar o exemplo que o professor nos mostrou em vídeo:

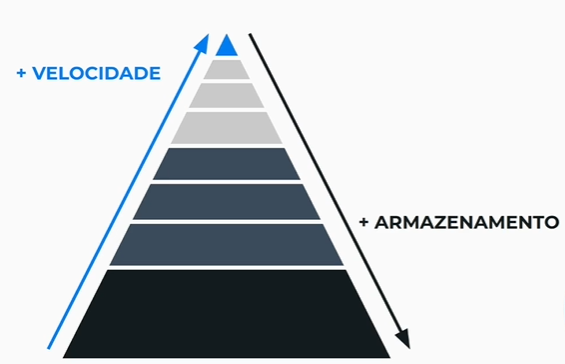

Vale ressaltar que a hierarquia de cache também é importante para o desempenho do acesso. A organização da cache está em quanto maior (mais perto do topo) mais velocidade temos e quanto mais descemos mais armazenamento temos.

E essa hierarquia é fundamental para diminuir o acesso do processador à memória principal, permitindo uma velocidade maior na execução dos programas.

Espero que as explicações aqui dadas tenham te ajudado a compreender melhor sobre a velocidade de acesso.

Qualquer dúvida que surgir, estarei à disposição!